CST MWS微帶線定向耦合器模擬

各位大神,小弟最新仿真微帶線定向耦合器,設計預期為中心頻率3GHz,耦合度20dB,遇到端口設置時有些糾結。

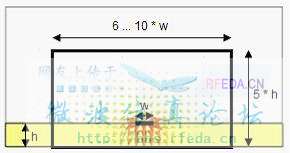

看了一些關于端口設置的說法,第一種是如下圖,端口寬度為微帶線的6到10倍,高度為基板厚度的5倍。但我畫的結構就算按端口寬度為6倍線寬來畫都會產(chǎn)生重疊。

第二種就是依靠2011版之后的版本自動計算端口的功能。計算出來k=7.39。按照這種方式也會使兩個端口產(chǎn)生重疊。

問題一:這種情況下的波導端口該如何設置才能得到比較準確的結果?

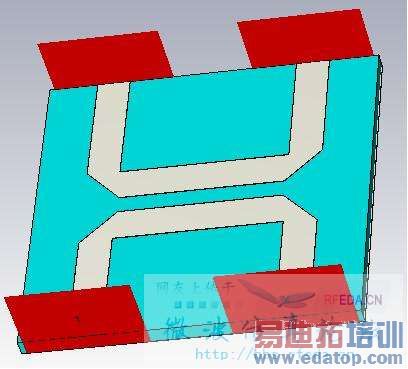

在無法確定波導端口尺寸的情況下,嘗試了用多芯端口設置

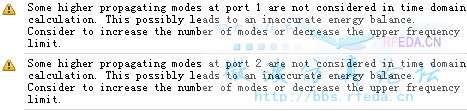

計算時會有警告說有高次模,讓減小端口尺寸或者降低頻率上限,否則結果可能不準。對于這個現(xiàn)象,我在做3dB分支線耦合器的范例時也會遇到這種警告,所以問題二:在這種情況下,是否會影響模擬結果,該怎么設置較為合適?多芯端口的高度是否與前面計算的波導端口的一樣高?

由于缺乏經(jīng)驗,對CST了解不深,不知道其他的設置有什么不妥的地方?jīng)],請各位大神一一指正。

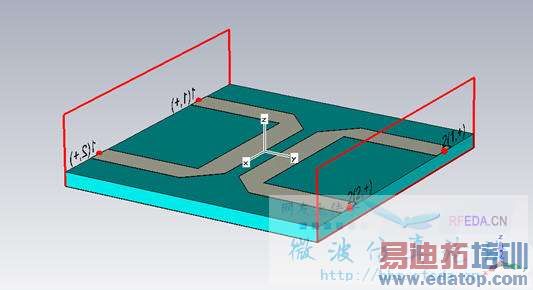

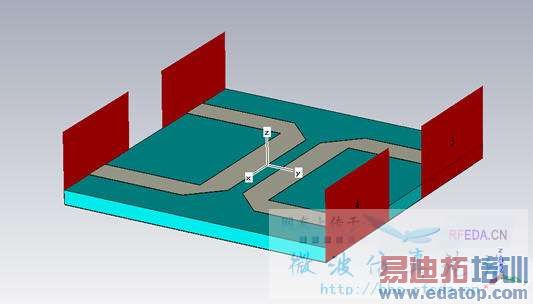

附我的模型圖,軟件版本CST 2009.

對于這種情況,應該是兩種端口都可以

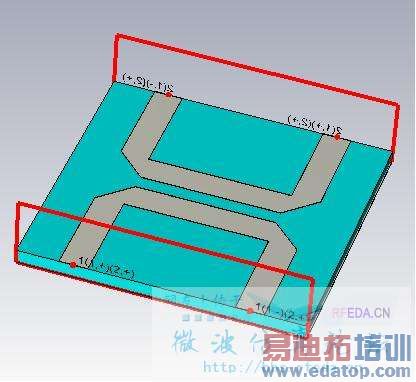

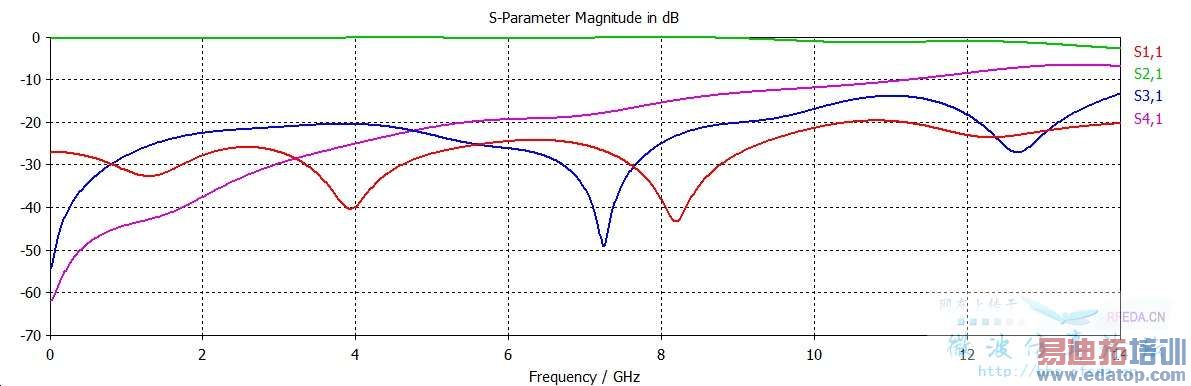

比不是一定要按照軟件說明來做。要變通,對此設想進行了驗證,如下:

說明這兩種端口完全是可以等效的

另:更改了你的設置,頻段設置0-14GHz就可以了啊,為什么設置了個0.0003?

為了偷懶,網(wǎng)格使用了自適應。

頻段設置:因為中心頻率是3GHz,所以之前頻率范圍設在0-5GHz。后來因為做出樣品,用網(wǎng)分測試了下,有差距,就改成網(wǎng)分的頻段300k-14GHz了,忘了改回來。

你的端口是怎么設置的,可否詳細說下?

或者勞煩把修改的模型發(fā)我一下。

多個端口的不用我說了吧?

多芯端口和你那個設置的方法一樣,只是設置兩個單獨的模式而已,不是像你的那種,一個差模一個共模

我想知道端口的尺寸設置大師用的是多少以及為什么這樣用就合適。 之前在做3dB分支線耦合器的范例是,采用的是差模和共模的激勵方式,所以我自己在做的時候就沿用了,但不清楚為什么這么用。在這個模型中,采用單獨模式和共差模有什么區(qū)別呢?我基礎不是很好,有點跟不上,見諒。或者有可借鑒的范例,告訴我一下。

多個端口時,端口比微帶線兩邊寬4.5,高6

我也不是很學術,我只能通俗的講,單獨模式,相當于多芯端口中的每個芯進行激勵,而共模和差模都是兩個芯同時激勵,只是共模時兩個芯的場是一樣的,差模時兩個芯的場是相反的

大師,你在選擇端口尺寸時是怎么考慮的。高為6符合原帖所述端口設置第一種思路,兩邊加寬4.5又是怎么來的呢?如你所述,端口尺寸兩邊加寬4.5,高為6,0-14GHz,自適應網(wǎng)格,T求解器。模擬出來的結果如圖:

跟你的圖好像還有差距,不知道還有什么方面是我沒注意到的沒?仿真時出現(xiàn)高次模未考慮,讓增加模式數(shù)或者降低頻率上限的警告。不知是否有辦法解決。

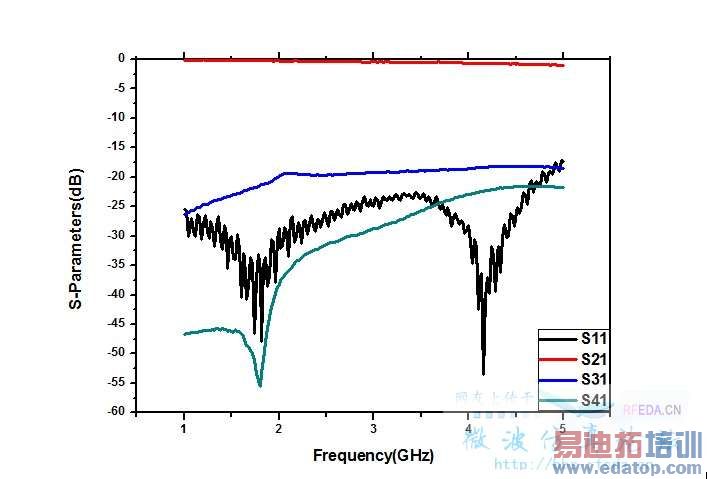

而根據(jù)我做的實際器件的測量結果如圖:

兩者趨勢較為相似,但符合得還不是很好,設置方面是否還有改進的余地?

兩邊的寬邊4.5是因為你的模型就這么大,再加就超出介質板的范圍了。

至于實測和仿真的對比,只能提醒你

1、檢查測試的正確性

2、檢查仿真的真實性,結構尺寸是否正確?測試時是否有殼體之類的

仿真并不會和實測完全對上,仿真是理想情況(尺寸絕對精確,材料理想)的仿真,而實物,是由各種誤差的,比如尺寸的精度,比如介質板的介電常數(shù)均勻度等等,仿真更多的時候是趨勢仿真,預估產(chǎn)品的性能,告訴你更改哪些參數(shù)會改變哪些性能,想要仿真出來的結果和測試完全一樣,幾乎是不可能的

大牛們!