CST電源濾波電路仿真四:電容耦合仿真

來源:CST仿真專家之路

更新時間:2024-09-03

閱讀:

作者 | Zhou Ming

*圖片來源于網絡

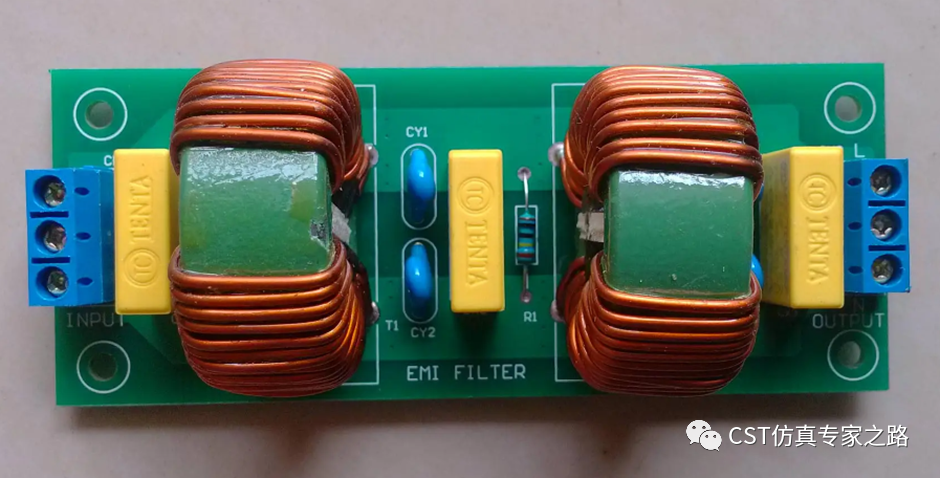

對于大多數EMC仿真的初學者來說,從EMI濾波電路仿真開始入手是一個非常好的選擇。傳統的電路仿真可以計算理想情況下濾波電路的插損,但無法考慮PCB走線、器件布局、電容接地位置以及器件之間耦合的影響,所以仿真精度非常低。相比純電路仿真,CST的3D仿真可以考慮上述所有因素的影響,從而得到非常精確的結果。

今天我來給小伙伴介紹CST電源濾波電路仿真(四)——電容耦合仿真。

1、選擇標稱容值3.3uF的薄膜電容,其內部結構如下圖所示,兩端分別是金屬Pin腳,兩極間有多層薄膜電極互相疊卷在一起,中間有電介質材料隔離。

2、了解電容內部結構后,開始創建電容的3D模型,主要包括繞制的金屬薄膜電極、兩側Pin腳以及中間的介質材料。

3、利用CST的低頻Es求解器可以很方便的計算容值,仿真出的結果是3.29uF,非常接近電容的規格3.3uF。

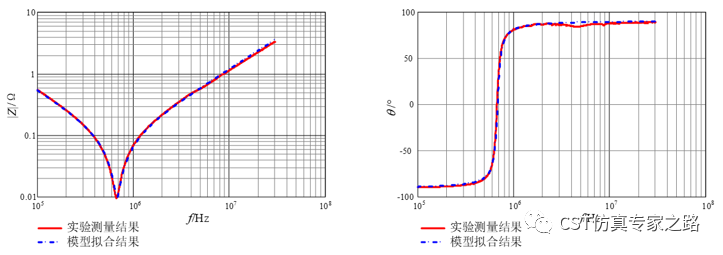

4、接下來我們仿真電容的阻抗曲線,這時候切換到高頻F求解器。在構建3D模型的時候,要特別注意兩側Pin腳的長度以及連接位置,盡量做到與實際一致。從CST的仿真結果來看,仿真和測試結果的一致性非常好。

已有的電容曲線測試和擬合結果

CST 3D仿真結果

CST仿真vs測試 對比

5、接下來我們在電容附近再增加一個電感模型,模擬電容與電感之間耦合的場景,分別對比電感水平放置和垂直放置兩個不同方向的耦合。

從仿真結果來看,場景2的耦合要明顯強于場景1,這對于在器件布局階段,如何選擇最優的擺放方向有很大的指導意義。